Perfect — here’s a clean, professional version of your FIFO README without emojis, while keeping it structured and polished:

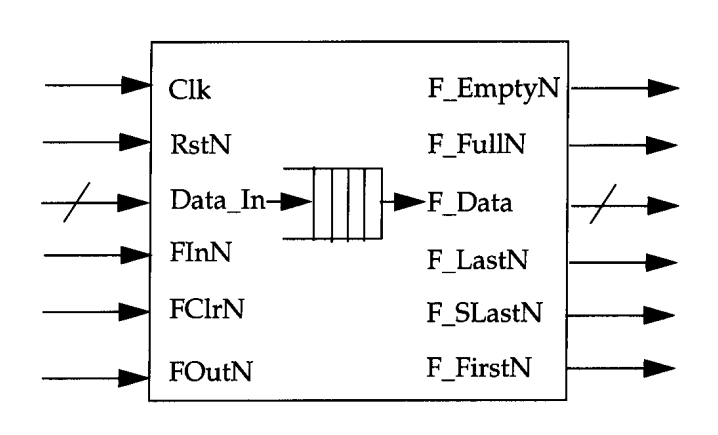

This repository contains a complete Verilog implementation of a synthesizable FIFO (First-In-First-Out) Model, supporting parameterized data width and depth, robust status flags, and a comprehensive testbench for verification.

This project implements a synchronous FIFO buffer with configurable parameters:

- Parameterized data width (

FWIDTH) and depth (FDEPTH) - Separate memory block module for data storage

- Comprehensive testbench validating all edge cases

- Real-time status flags to monitor FIFO condition

Note: All signals ending in N are active low.

| Port Name | Description |

|---|---|

Clk |

Clock signal |

RstN |

Reset signal |

Data_In |

32-bit input data to FIFO |

FInN |

Write-enable signal |

FClrN |

Clear FIFO |

FOutN |

Read-enable signal |

| Port Name | Description |

|---|---|

F_Data |

32-bit output data from FIFO |

F_FullN |

FIFO is full |

F_EmptyN |

FIFO is empty |

F_LastN |

Space left for one more data value |

F_SLastN |

Space left for two more data values |

F_FirstN |

Only one data value remains in FIFO |

-

Parameterization: Configurable FIFO width & depth using macros (

FWIDTH,FDEPTH) -

Synchronous Design: Both write and read synchronized to the clock

-

Modular Architecture: Dedicated memory block for clean design separation

-

Status Flags:

F_EmptyN→ FIFO is emptyF_FullN→ FIFO is fullF_FirstN→ Only one element leftF_LastN→ One space leftF_SLastN→ Two spaces left

-

Robust Testbench: Tests all operational and boundary conditions

- Controls FIFO logic (read/write pointers, counter)

- Generates status signals

- Implements synchronous memory storage

- Controlled writes, asynchronous reads

- Comprehensive testbench

- Stimuli generation and flag verification

The testbench verifies FIFO functionality through:

-

Clock generation and reset sequencing

-

Continuous writes until FIFO is full

-

Validation of full and overflow conditions

-

Continuous reads until FIFO is empty

-

Validation of empty and underflow conditions

-

Status flag checks:

F_FirstN→ One element leftF_SLastN→ Two spaces leftF_LastN→ One space left

Verbose output is generated using $display for debugging.

This design can be simulated with:

- ModelSim

- Vivado XSIM

- Verilator

- Synopsys VCS

# Compile all source files

vlog FIFO_MEM_BLK.v FIFO_Model.v FIFO_Model_tb.v

# Simulate

vsim FIFO_Model_tb